가상 메모리와 현대 컴퓨터 시스템의 속도를 책임지는 숨은 영웅, TLB에 대한 심층 분석입니다. 페이지 테이블 조회의 어려움과 TLB가 어떻게 그 문제를 해결하는지, 그리고 컨텍스트 스위칭과의 관계까지 샅샅이 파헤쳐 보겠습니다.

TLB: 페이지 테이블의 번거로움을 해결하는 마법의 캐시

페이지 테이블은 가상 주소를 물리 주소로 바꿔주는, 마치 사전 같은 존재입니다. 프로그램은 가상 주소로 메모리에 접근하려 하지만, 실제 컴퓨터는 물리 주소를 알아야 데이터를 찾을 수 있습니다. 그래서 가상 주소를 물리 주소로 변환하는 과정이 필요하며, 이 과정에서 페이지 테이블이 사용됩니다. 하지만 페이지 테이블을 메모리에서 찾는 것은 시간이 꽤 걸립니다. 매번 페이지 테이블을 뒤져야 한다면 컴퓨터 속도가 얼마나 느려질까요?

그래서 등장한 것이 바로 TLB입니다. TLB는 Translation Lookaside Buffer의 약자로, 페이지 테이블의 내용을 미리 캐싱해 놓는 작은 고속 메모리입니다. CPU는 메모리에 접근하기 전에 먼저 TLB를 확인합니다. 만약 TLB에 필요한 정보가 있다면(TLB 히트!), 페이지 테이블을 뒤질 필요 없이 바로 물리 주소를 얻을 수 있습니다. 하지만 TLB에도 없는 경우(TLB 미스!)에는 어쩔 수 없이 페이지 테이블을 뒤져야 합니다.

하지만 TLB 덕분에 페이지 테이블을 직접 찾는 횟수가 훨씬 줄어들고, 결과적으로 시스템의 전체적인 성능이 크게 향상됩니다. TLB는 컴퓨터의 속도를 엄청나게 높여주는 숨은 영웅과 같습니다. 이 작은 캐시가 어떻게 이런 놀라운 효과를 내는지 신기합니다. 하지만 이 마법의 비결은 단순히 최근에 접근했던 페이지 정보들을 저장하고 관리하는 효율적인 알고리즘에 있습니다.

TLB의 크기는 제한적이기 때문에 모든 페이지 테이블 엔트리를 저장할 수는 없습니다. 그래서 TLB는 일반적으로 LRU(Least Recently Used) 알고리즘과 같은 캐시 교체 알고리즘을 사용하여 가장 오랫동안 사용되지 않은 엔트리를 제거하고 최근에 사용된 엔트리를 저장합니다. 이러한 메커니즘 덕분에 TLB는 최신 정보를 효율적으로 유지하고, 시스템 성능을 최대한으로 높일 수 있습니다.

TLB의 효율성은 메모리 접근 패턴, 즉 지역성(Locality) 원리와 밀접한 관련이 있습니다. 프로그램은 보통 특정 영역의 메모리에 반복적으로 접근하는 경향이 있는데, 이러한 지역성 덕분에 TLB 히트율이 높아지고, 결과적으로 시스템 성능이 향상됩니다. 이러한 지역성 원리를 이용해서 TLB는 최고의 성능을 발휘합니다.

TLB의 구성 요소와 작동 방식: 하드웨어와 소프트웨어의 조화

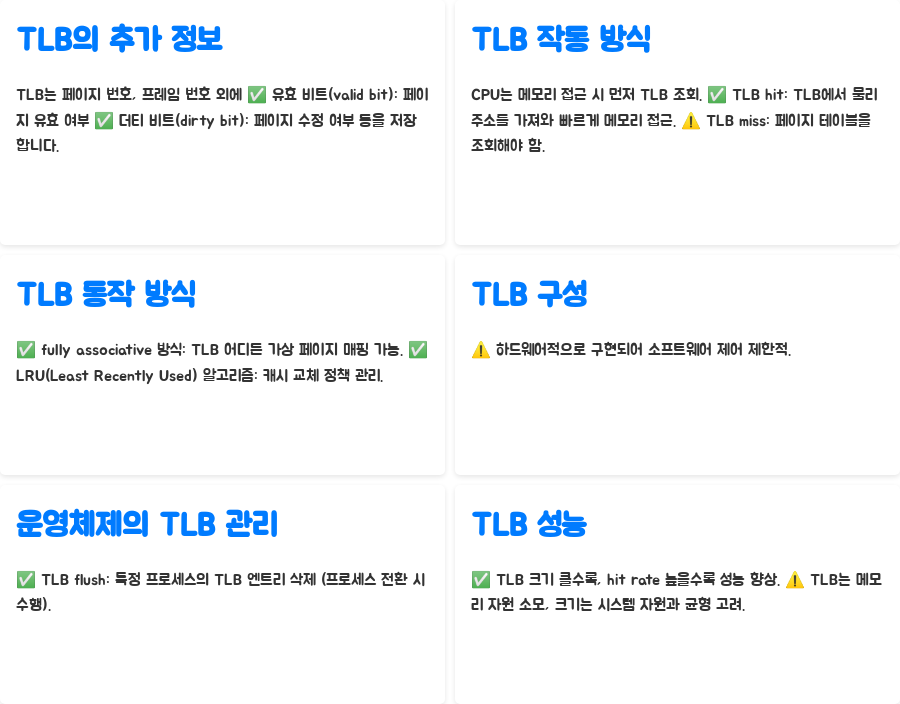

TLB는 단순히 페이지 번호와 프레임 번호만 저장하는 것이 아니라, 페이지 테이블 엔트리(PTE)의 다른 중요한 정보들도 함께 저장합니다. 예를 들어, 페이지가 유효한지 여부를 나타내는 유효 비트 (valid bit), 페이지가 수정되었는지 여부를 나타내는 더티 비트 (dirty bit) 등이 있습니다. 이러한 추가 정보들은 페이지의 상태를 빠르게 확인하고 메모리 관리에 필수적인 정보를 제공합니다.

TLB의 작동 방식은 매우 효율적으로 설계되어 있습니다. CPU는 메모리 접근을 요청할 때, 먼저 TLB를 조회합니다. 만약 TLB에 해당하는 엔트리가 있다면 (TLB hit), CPU는 TLB에서 직접 물리 주소를 가져와 메모리에 접근합니다. 이 과정은 매우 빠르게 진행되므로 시스템 성능 향상에 크게 기여합니다. 하지만 TLB에 해당 엔트리가 없다면 (TLB miss), CPU는 페이지 테이블을 조회해야 합니다.

TLB는 일반적으로 fully associative 방식으로 동작합니다. 이는 TLB 내의 어떤 위치에도 임의의 가상 페이지 번호를 매핑할 수 있다는 것을 의미합니다. 이러한 방식은 TLB의 유연성을 높이고, 다양한 메모리 접근 패턴에 효율적으로 대응할 수 있도록 합니다. 또한 TLB는 보통 LRU(Least Recently Used) 알고리즘을 이용하여 캐시 교체 정책을 관리합니다.

TLB의 구성 방식은 하드웨어적으로 구현되어 있기 때문에 소프트웨어적인 제어가 제한적입니다. 하지만 운영체제는 TLB의 관리에 영향을 미칠 수 있는 몇 가지 기능들을 제공합니다. 예를 들어, TLB flush는 특정 프로세스의 TLB 엔트리를 모두 삭제하는 작업입니다. 이 작업은 주로 프로세스 전환 시에 수행되며, 다른 프로세스의 주소 공간과의 충돌을 방지하는 데 중요한 역할을 합니다.

TLB의 성능은 하드웨어 설계와 운영체제의 정책에 따라 크게 달라집니다. TLB의 크기가 클수록, 그리고 TLB hit rate가 높을수록 시스템 성능이 향상됩니다. 하지만 TLB는 메모리 자원을 소모하기 때문에 TLB 크기는 시스템 자원과의 균형을 고려하여 결정되어야 합니다.

TLB와 컨텍스트 스위칭: 프로세스 전환의 효율성 극대화

컨텍스트 스위칭은 운영체제가 하나의 프로세스에서 다른 프로세스로 전환하는 과정입니다. 각 프로세스는 독립적인 가상 메모리 공간을 가지고 있으므로, 프로세스 전환 시에는 TLB에 저장된 이전 프로세스의 정보를 지우고 새로운 프로세스의 정보로 갱신해야 합니다. 이 과정이 바로 TLB flush입니다.

TLB flush는 매우 중요한 작업입니다. TLB flush를 수행하지 않으면 이전 프로세스의 가상 주소가 새로운 프로세스의 주소 공간과 충돌할 수 있고, 이는 시스템의 안정성에 심각한 문제를 일으킬 수 있습니다. 그러니 TLB flush는 마치 시스템 안전을 위한 안전장치와 같습니다.

일부 시스템에서는 TLB flush 대신 **ASID (Address Space Identifier)**를 사용하여 프로세스의 주소 공간을 구분하기도 합니다. 각 프로세스에 고유한 ASID를 할당하고 TLB 엔트리에 ASID 정보를 저장함으로써, 프로세스 전환 시에 TLB 전체를 flush하지 않고도 이전 프로세스의 엔트리만 선택적으로 제거할 수 있습니다.

컨텍스트 스위칭 과정은 TLB flush와 밀접한 관련이 있습니다. 일반적으로 컨텍스트 스위칭은 다음과 같은 단계를 거칩니다. 먼저 현재 프로세스의 상태를 저장하고 그 후 새로운 프로세스의 상태를 로드합니다. 이 과정에서 TLB flush가 수행되고 새로운 프로세스의 페이지 테이블 엔트리가 TLB에 로드됩니다.

컨텍스트 스위칭 속도는 시스템 성능에 큰 영향을 미칩니다. TLB flush는 컨텍스트 스위칭에 소요되는 시간에 영향을 미치는 중요한 요소입니다. 효율적인 TLB 관리 기법을 통해 컨텍스트 스위칭 속도를 높일 수 있으며, 이는 곧 시스템 전체 성능 향상으로 이어집니다.

| TLB | 페이지 테이블 캐시 | 빠른 주소 변환 | 크기 제한 |

| TLB 히트 | TLB에 정보 존재 | 빠른 메모리 접근 | |

| TLB 미스 | TLB에 정보 없음 | 페이지 테이블 조회 필요 | 느린 메모리 접근 |

| TLB Flush | TLB 내용 삭제 | 컨텍스트 스위칭 안정성 확보 | 성능 저하 가능성 |

| ASID | 주소 공간 식별자 | TLB flush 없이 프로세스 전환 가능 |

기능 설명 장점 단점

Q1. TLB 미스가 발생하면 성능 저하가 심각한가요?

A1. 네, TLB 미스는 페이지 테이블을 직접 참조해야 하므로 메모리 접근 시간이 늘어나 성능 저하를 야기합니다, 하지만 TLB는 메모리 접근의 지역성을 이용하여 히트율을 높이도록 설계되었기 때문에 실제 성능 저하 정도는 생각보다 크지 않은 경우가 많습니다.

Q2. TLB flush는 언제 발생하나요?

A2. TLB flush는 주로 프로세스 전환(컨텍스트 스위칭) 시 발생합니다, 각 프로세스는 독립적인 주소 공간을 가지므로 이전 프로세스의 주소 매핑 정보가 남아 있으면 안되기 때문입니다, 또한 특정 시스템 호출이나 예외 상황에서도 TLB flush가 발생할 수 있습니다.

Q3. TLB의 크기는 어떻게 결정되나요?

A3. TLB의 크기는 하드웨어 설계 시 결정되며 시스템 자원과 TLB hit rate 간의 절충점을 고려하여 결정됩니다, TLB가 너무 작으면 미스율이 높아지고 너무 크면 자원 낭비가 발생합니다, 따라서 최적의 크기를 찾는 것이 중요합니다.

이 글이 TLB에 대한 이해를 돕는데 도움이 되었기를 바랍니다, 궁금한 점이나 추가적인 질문이 있다면 언제든지 댓글을 남겨주세요, 다음에는 더욱 유익한 내용으로 찾아뵙겠습니다.